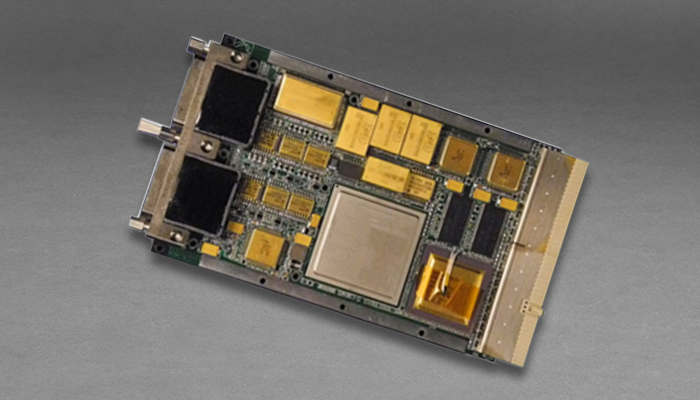

AJEET SBC with Xilinx V5 FPGA

Jump To:

Features

Literature

Related

Functions

- Radiation-Hardened BRE440 SoC PowerPC Processor @100MHz Core Frequency

- Radiation-Hardened Xilinx Virtex-5QV FPGA

- 512Mbytes Double Data Rate (DDR) SDRAM System Memory (EDAC)

- 128Kbytes Boot EEPROM (TMR)

- Up to 8Gbyte FLASH Memory (TMR) with independent switched power

- 256Mbytes Digital Signal Processing (DSP) SDRAM (EDAC/Reed-Solomon capable)

- PCI V2.2, 32/64-bit, 33/66 MHz, configurable for cPCI system slot or peripheral slot operation; Initiator and target operation

- Mass: 460g, Power: 11.7W, TID: 50KRad

- Qty 24 RS422 or LVDS inputs

- Qty 24 RS422 or LVDS outputs

- Qty 2 RS485 transceivers

- Qty 1 LVDS DeSerializers (3:21)

- Qty 16 Bi-Level inputs (TTL/CMOS), 5V or 3.3V

- Qty 80 Analogs (+/-10V) / AD590 Temps (16 can be PRTs) with 14 AD590 voltage excitations

- Qty 12 Sun Sensors with 3 Sun Sensor Current Excitations

- Support for 10/100 Mbps RMII Ethernet (Requires 3 LVDS TX, 4 LVDS RX)

- Support for SpaceWire Interfaces (Requires 2 LVDS TX, 2 LVDS RX per interface)

| Feature | AJEET Capability | Comment |

| CPU | IBM PPC 440 core with FPU, 100MHz Core Frequency | VxWorks 6.7 BRE-Boot BSP Included |

| L1 (Data and Instruction) cache | 32Kbyte each | |

| L2 Cache | 256Kbyte | |

| DMA | 4 Channels | |

| Ethernet | 2 Channels, RMII (10/100) | LVDS Buffers. Interface unit for ground testing can be purchased as an option. |

| UART | 2 Channels | RS422 Buffers |

| PCI | 33MHz, 32 bit cPCI Interface | |

| Boot Code Storage | 128Kbytes EEPROM | Triple Module Redundant (TMR) |

| SW Code Storage | 1GKbytes Flash | Triple Module Redundant (TMR) |

| System Memory | 512Mbytes DDR | EDAC protected |

| DSP and I/O Memory | 256Mbytes SDRAM | EDAC protected/Reed-Solomon capable. Can be used for Xilinx data processing |

| User Defined FPGA resource | Rad-Hard Xilinx Virtex-5 (SIRF) | On-Orbit reprogrammable |

| High Speed data interface | 1 LVDS DESER (3:21) interface | Up to 800Mbps data transfer link |

| User Defined digital I/O | 2 RS485 buffers |

Connected to Xilinx FPGA for flexibility |

| User Defined digital I/O | 24 RS422/LVDS TX and 24 RS422/LVDS RX |

Connected to Xilinx FPGA for flexibility. Additional Ethernet interfaces are supported (each requires 3 LVDS TX, 4 LVDS RX) SpaceWire interfaces are supported (each requires 2 LVDS TX, 2 LVDS RX) Note: Some of these RS422 buffers are used for UART and Ethernet interfaces. |

| User Defined discrete signals | 16 TTL/CMOS Inputs | Discrete to monitor relay etc., status |

| User Defined Analog I/O | 80 Analogs / AD590 Temps, 12 Sun Sensors for SOH |

Up to 16 AD590 inputs can be configured for PRTs. Analog I/Os are on AJEET daughter board that can be removed if not required. |